【酒酒】数字IC手撕代码总结,1. 用任意语言写1:100的质数(7.17) 2 2. 奇数分频(三分频)(7.18) 3 3. 偶数分频(二分频)(7.19) 5 4. 画出可以检测10110串的状态转移图,要求每检测到一次该序列,输出两个...

”数字IC 手撕代码 面试“ 的搜索结果

平头哥的手撕代码很有意思,平头哥技术终面手撕真题,题目描述如下:输入clk,每个时钟输入1比特的data_in,然后进来之后的序列是每次左移,也就是如果第一个时钟data_in=1,第二个时钟datain=0,第三个时钟data_in=1;...

其无非就是三种可能当我第一次接触握手信号的时候,其实是很清楚上面的三条握手原则的,但是具体的,master和slave之间的握手信号该怎么写代码却迷迷糊糊。就利用这篇文章简单的讲一下master和slave之间是怎么通过...

数字IC面试手撕代码(十一)

标签: 数字IC设计

题目:设计一个序列发生器,它能产生如下序列: 010110111011110111110111111… 思路:设计两个状态S0,S1,以及两个计数器count和state_count, S0状态只持续一个周期,S1状态当且仅当state...代码 module sequence_gen

题目 输入一个01序列,当valid为高时输入比特...代码实现 module top( input logic clk, input logic rst, input logic bit_in, input logic bit_valid, output logic bit_out, output logic bit_ovalid ); logi

这是每个公司对于数字IC设计人员的面试考题,是近些年来公司经常出现的一些考题。

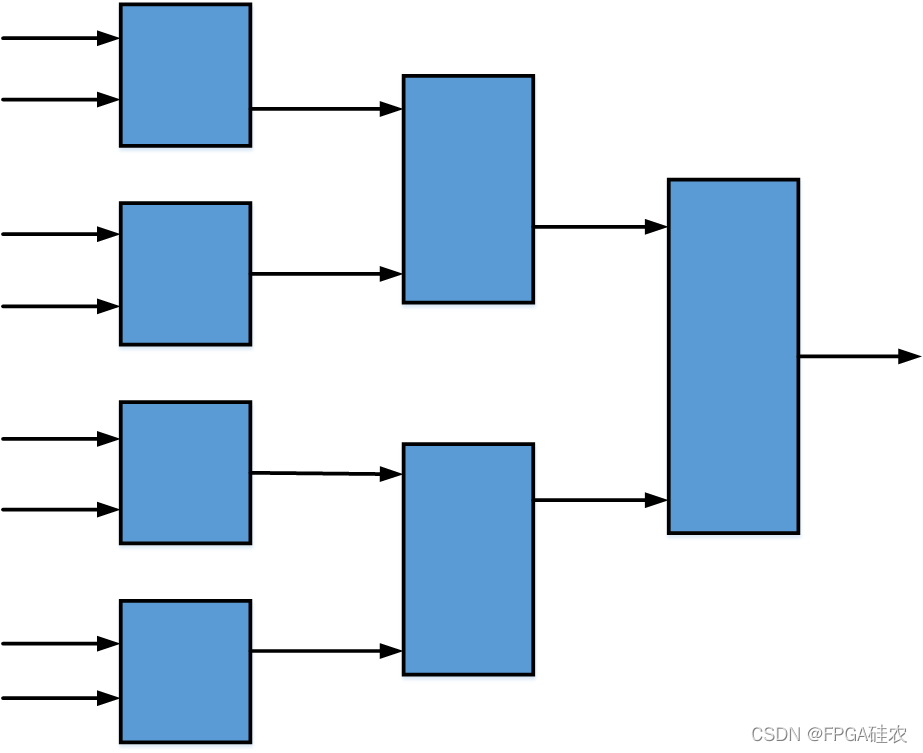

以上是泰凌微公司的笔试真题,手撕一个代码,题目描述如下:假设每个clock cycle输入是一个3-bit数据信号,现在需要按次序整形成5-bit数据信号输出,并给出valid信号。其中LSB First,请用Verilog/VHDL给出代码。该...

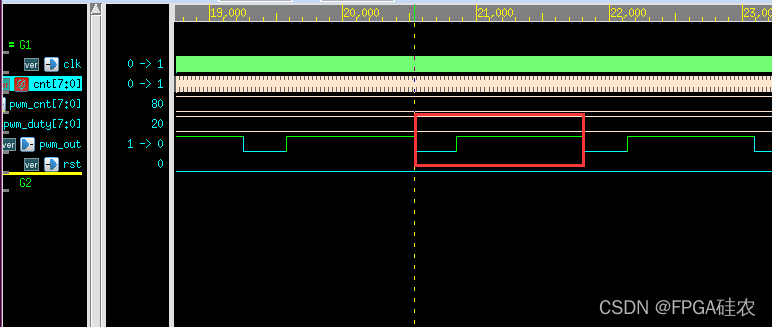

再简单来说,让你手撕一个四分频电路,就是写代码生成一个周期是原来四倍的时钟,如果手撕一个三分频电路,就是写代码生成一个周期是原来三倍的时钟。如上图所示,就是一个四分频电路的波形,四分频后,新的clk_out...

..持续更新更多手撕代码题可以前往。

现有一时钟周期为20ns的时钟,他们的关系如下图所示,请写出计算该脉冲个数的verilog代码。ps:如果有人有更好的方案相邻1ns的两个5ns pulse都能检测到的话,可以在评论区讲解自己的方法。约束:这种方法使用的前提...

数字IC面试手撕代码(七)

标签: 数字IC设计

题目 输入一个序列(每周期输入一个比特,高位先输入),判断当前接收到的bit所组成的无符号整数是否为3的倍数。例如 1:输出为0 10:输出为0 100:输出为0 1001:输出为1(模3为0) 方法 设当前接收到的比特所组成的...

这个不要背表达式,如果背表达式,正式手撕代码的时候很容易忘记,然后写错(虽然全加器很简单。)我们推导一下表达式。全加器的门电路就不画了,原理和半加器是一致的,信号有点多容易弄混,所以画的时候细心一点,...

本篇专栏记录数字IC秋招过程中的一些基础手撕代码,以及笔面试遇到的手撕代码真题。

再简单来说,让你手撕一个四分频电路,就是写代码生成一个周期是原来四倍的时钟,如果手撕一个三分频电路,就是写代码生成一个周期是原来三倍的时钟。如上图所示,就是一个四分频电路的波形,四分频后,新的clk_out...

在某个群看到某个大佬,面试海康数字IC实习的时候让手撕代码。现在也把这个题目复现一下。 题目正常情况下数据包由起始码(16bit)、数据段(n bytes n < 256 )、结束码(16bit)三部分组成。起始码为0xFF00、...

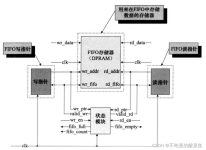

串转并的使用环境非常多,在接口处用到最多,在某些模块的输入仅允许串行输入时,而总线上的数时并行的,那就需要通过串并转换,把并行的数据转换成串行的数据,包括在输出的时候,需要把串行的数据转换成并行的数据...

题目 题目很简单,就是写一个10110序列发生器。 有两种方法,第一种就是通过循环移位的方式,来产生相应的序列,另一种方法则是通过状态机来实现。 方法一:循环移位 `timescale 1ns / 1ps /////////////////////////...

有限状态机(Finite state machine)是为研究有限内存的计算过程和某些语言类而抽象出的一种。有限状态自动机拥有,每个状态可以迁移到零个或多个状态,输入字串决定执行哪个状态的迁移。有限状态自动机可以表示为一...

问题:输入一个16bit的数,现在要求它除以3得到的商和余数?如何优化? 看到这个题目,第一个想到的方法就是最传统的减3,商加1,判断余数,然后一直减、一直加,直到最后的余数小于3,这个方法最蠢最直观。...

数字IC面试手撕代码(八)

标签: 数字IC设计

看看在不同状态下,流水线是否会出现数据传输错误或者数据丢失的情况。把整个模块包装成一个module后,我们这个就相当于一个流水处理一段长延时组合逻辑的IP。对于我们这个IP来说,valid_i和ready_o同时为高时,数据...

数字IC面试,FPGA面试手撕代码题全部收录,一共50道,详细讲解。

数字IC手撕代码(五)

标签: 数字IC面试

之前在群里看到别人说这样一个题目:在一串8bit数据流中,求去掉最大数据和最小数据的和。 module add_data( input clk, input rst_n, input [7:0] din, input din_vld, output reg [7:0] max_data, ...

输入为 i0,i1,i2,…,i253,i254,….占 1 个时钟周期, 输出 sum0 为 i0 +i2+….+i254 的加和值(隔点相加), sum1 为 i1+i3+….+i255,sum2 为 i2+i4+….+i256,如此下去,每个输出占一个时钟周期 Sum0 和 i0 的相对延时...

奇偶校验 奇偶校验,意思是判断一个向量的若干比特中,1的个数是奇数个还是偶数个,所谓奇校验,是指加上校验位后,使得整个数据中1的个数为奇数个,而偶数校验是指加上校验位之后,整个数据中1的个数为偶数个。...

推荐文章

- 联邦学习综述-程序员宅基地

- virtuoso--工艺库答疑_tsmc mac-程序员宅基地

- C++中的exit函数_c++ exit-程序员宅基地

- Java入门基础知识点总结(详细篇)_java基础知识重点总结-程序员宅基地

- 【SpringBoot】82、SpringBoot集成Quartz实现动态管理定时任务_springboot集成quratz 实现动态任务调度-程序员宅基地

- testNG常见测试方法_idea_java_testng 测试-程序员宅基地

- Debian11系统安装-程序员宅基地

- Centos7重置root用户密码_centos7更改root密码-程序员宅基地

- STM32常用协议之IIC协议详解_正点原子stm32 iic-程序员宅基地

- 【视频播放】Jplayer视频播放器的使用_jplayer 播放amr-程序员宅基地